Today, at the 2019 Symposia on VLSI Technology and Circuits (June 9-14, 2019), imec, a world-leading research and innovation hub in nanoelectronics and digital technologies, reports improved performance for both Ge-based n-type FinFETs and Ge-based p-type gate-all-around (GAA) devices. For Ge n-type FinFETs, pre-gate stack process optimization dramatically improved reliability and performance, with 100 percent improvement in positive bias temperature instability (PBTI) and improvement in GmSAT vs. SSSAT benchmark. For the Ge-based p-type GAA device, excellent short-channel control and performance were achieved with an improved extension-less junction scheme. The results confirm the potential of Ge-based CMOS transistors as high-performance solutions for the 3nm and beyond technology nodes.

Due to the higher intrinsic mobility of Ge compared to Si, Ge-based FinFET devices have emerged as non-disruptive performance boosters for future technology nodes. While Ge p-type FinFET devices have been extensively studied, the development of well-performing, reliable Ge n-type FinFET devices is lagging behind. Imec has now proposed an optimized process flow for the gate stack, solving one of the major challenges for Ge n-type FinFET development.

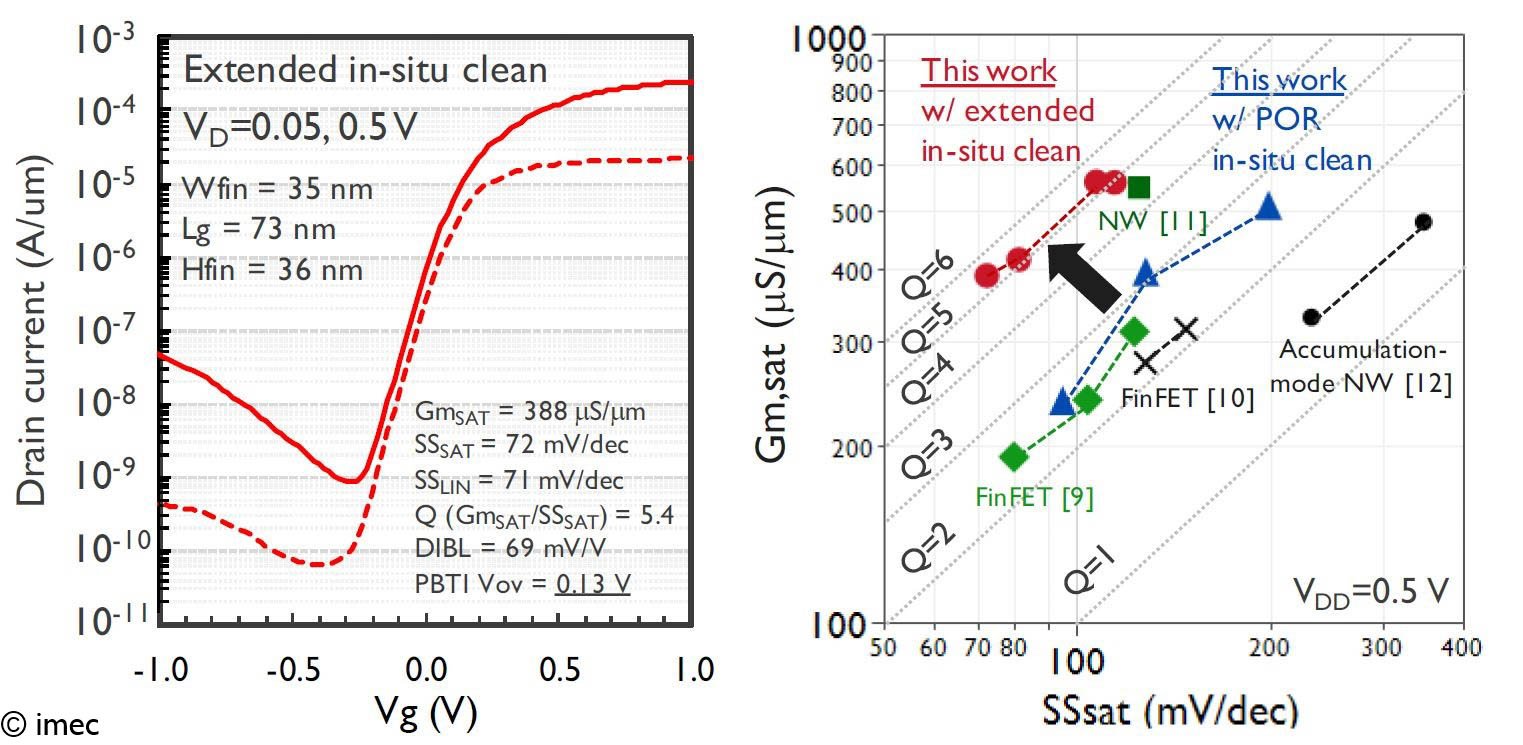

Key to the successful gate stack formation are an improved pre-cleaning and an optimized dummy gate oxide deposition and removal process, as part of a replacement metal-gate (RMG) process flow. Imec’s optimized process flow resulted in 100 percent improved positive bias temperature instability (PBTI) and a 100% improvement in GmSAT vs. SSSAT benchmark – a measure for the interface quality and electron mobility.

“With our process flow, the oxide-free Ge channel surface can be prepared prior to the gate and efficiently protected from oxidation”, explains Naoto Horiguchi, logic program manager at imec. “The paper describing these results was selected by the Committee members of the VLSI Symposium as a highlight 2019 VLSI technology paper. It underlines the importance of our improved dummy gate oxide process for the formation of high-performance and reliable Ge n-type FinFETs.”

In a second paper, imec proposes an improved junction scheme to solve one of the major challenges for p-type strained Ge-based GAA devices, i.e. achieving good short channel control while preserving transistor performance. A dramatic improvement in short channel control – allowing gate length scaling down to 25nm – was achieved by using an extension-less scheme, i.e., without dopant implantation in the ‘extension’ region next to the gate. To maintain the transistor’s performance, the extension-less scheme was combined with spacer thickness reduction, and with the implementation of highly boron-doped Ge or GeSn as source/drain material. The optimized process flow resulted in a 55 percent improvement in GmSAT Vs. SSSAT benchmark on Ge GAA devices as compared to previous work. Short channel (LG~25nm) device also shown excellent Gm (Gm,lin=512µS/µm, Gm,sat=2220µS/µm).

Naoto Horiguchi: “Ge GAA devices have the potential to further extend gate length scaling beyond what is possible with Ge-based FinFETs. They can be fabricated by using a process flow that is not so disruptive compared to FinFET processing. And much of the learnings we obtain from FinFET development can be transferred to GAA devices. By using our extension-less scheme, we have now demonstrated the feasibility of these Ge-based GAA devices for gate length scaling down to 25nm, while preserving excellent performance.”