Unleash new levels of compute performance with vertical power delivery

As high-performance AI processor power levels continue to rise and core voltages decline with advanced process nodes, power system designers are challenged with managing ever-increasing power delivery network (PDN) impedance voltage drops, voltage gradients across high-current, low-voltage processor power pins, transient performance specifications and power loss.

In the case of clustered computing, where tightly packed arrays of processors are used to increase the speed and performance of machine learning, PDN complexity rises significantly as current delivery must be done vertically from underneath the array.

Designing a PDN using the Vicor Factorized Power Architecture (FPA™) with current multipliers at the point-of-load instead of legacy voltage averaging techniques, allows a significant step up in performance. This is enabled by the characteristics of point-of-load (PoL) power components: high current density, reduced component count and very importantly, flexibility in placement. PoL power components thus enable current to be delivered laterally and/or vertically to AI processor core(s) and memory rails, significantly minimizing PDN impedances.

Understanding the peak current demands with today’s power delivery networks

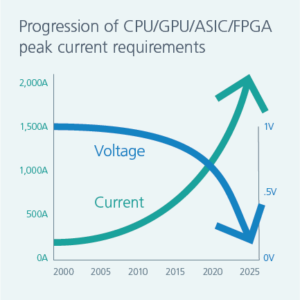

Modern day GPUs have tens of billions of transistors, a number which is growing with every new generation and product family and which is made possible by smaller process node geometries. Enhancements in processor performance then follow with every new generation, but this comes at the price of exponentially increased power delivery demands. Figure 1 shows the dramatic increase in current requirements due to reduced transistor geometry and core voltages.

Figure 1 — In most cases, power delivery is now the limiting factor in computing performance as new processors consume ever increasing currents. Power delivery entails not just the distribution of power but also the efficiency, size, cost and thermal performance.

Peak current demands of up to 2000A are now a typical requirement. In response to this power delivery challenge some xPU companies are evaluating multi-rail options where the main core power rails are split into five or more lower-current power inputs. The PDN for each of these rails must still deliver a high current while also needing individual tight regulation, which puts pressure on the density of the PDN and its physical location on the accelerator card.

To further add to this complexity, the highly dynamic nature of machine learning workloads, result in very high di/dt transients lasting several microseconds. This creates stress across the PDN of a high-performance processor module or accelerator card.

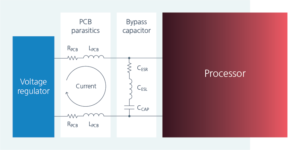

The architecture of a typical power delivery network is highlighted in Figure 2.

Figure 2 — Typical high-performance processor PDN

Best practices for optimizing the power delivery network

The work by the Open Compute Project® (OCP®) consortium has helped establish a framework of standards for designing rack- and card-based processor developments. The Open Rack Standard V2.2 defines a 48V server backplane and a 48V operating voltage for open accelerator modules (OAMs) used predominately for artificial intelligence (AI) and machine learning workloads. To maintain compatibility with legacy 12V systems, the standard stipulates the ability to meet 12-to-48V and 48-to-12V requirements.

Focusing on powering the processor, or PoL, is fraught with technical challenges. The technical advances highlighted in the previous section focused on the downward trend of voltage scaling, the requirement for tight core voltage tolerance and the upward trend of current consumption. At the board level, the impact of these factors manifests in multiple ways.

The peak current densities encountered are extreme for any PCB. Routing power paths capable of these huge loads demands careful attention. Highly dynamic workloads can create spiking voltage transients, which sophisticated processors find disruptive and potentially damaging. Yet, a processor board has hundreds of other passive components, memory and other ICs essential to its operation that also need placement.

Then there are the I2R losses. Power path trace lengths need to be short. To achieve this the power conversion modules should be close to the processor to reduce trace heating. The likelihood of PCB flexing due to the processor load currents and localized thermal gradients of the processor demand board stiffeners.

Also, the converter’s power efficiency specification should be as high as possible to prevent further thermal management challenges.

Unleashing the power of the processer

Delivering enough power to the processor today needs innovation to try to get ahead of the status quo. New ideas, architectures, topologies and technologies are the path to a more reliable, scalable power delivery network. The Vicor Factorized Power Architecture (FPA™) is the foundation for delivering more efficient power for today’s unprecedented high-performance computing demands.

Figure 3 — Factorized Power Architecture (FPA™) factorizes the power into the dedicated functions of regulation and transformation. Both of these functions can be optimized and deployed individually to provide a high-density and high-efficiency solution.

The Vicor FPA divides the task of a power converter into the dedicated functions of regulation and transformation. A high-efficiency, high-density solution is achieved by separating them and optimizing them individually. FPA in conjunction with the Sine Amplitude Converter (SAC™) topology underpins several innovative architectures that can help unleash the full power of today’s high-performance processors.

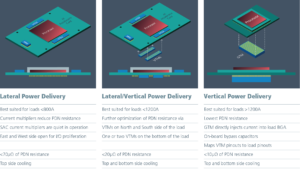

Figure 4 — Leveraging FPA, Vicor minimizes the “last inch” resistances with several patented solutions involving lateral power delivery (LPD) and vertical power delivery (VPD). All enable processors to achieve previously unattainable performance levels to support today’s exponentially growing HPC processing demands.

Vicor power converter technology takes advantage of an unique Factorized Power Architecture that not only optimizes the power converter efficiency but also enables very low PDN losses associated with low-voltage, high-current power delivery to the PoL (ASIC or a CPU or a GPU etc..)

Lateral power delivery is an innovative technique where the two current multipliers (Vicor VTM™ modules) flank the north and south side or the east and west side of the processor. This technique is preferable for load currents of ~800A at 0.8V nominal with an associated 70µΩ of PDN at 100°C. Using these numbers, we can compute ~45W of power loss. A heat sink that covers both the 2.8mm tall current multipliers and the processor as shown in the picture would be a good thermal solution. This architecture is excellent for powering graphics accelerator cards (OAM or otherwise), networking ASICs and APUs used in hyperscale data centers or supercomputer cabinets.

The Lateral-vertical power delivery technique is similar to lateral power delivery, but with this difference: only 70% of the power is delivered laterally using the current multipliers that flank the sides of the processor. An additional current multiplier on the bottom side of the processor will deliver the remaining 30% of the load current directly to the processor BGA. The hybrid of lateral and vertical achieves a reduction in PDN loss by almost a factor of four! This technique also frees board space to accommodate a second high-current rail (aux) or HBM memory rails on the top side of the board around the processor.

Vertical-lateral power delivery, on the other hand, takes advantage of pushing >50% of the load current through additional current multipliers on the bottom side of the processor. This technique enables a further 50% reduction in PDN loss compared to the lateral-vertical approach. A 1200A design can now realize a PDN resistance of a mere 10µΩ, resulting in fewer than 14.4W of power loss. In this case, heat sinks can be placed on both the top and bottom sides of the load as space permits. This architecture is especially effective for applications that cannot afford power components on the top side of the board in order to accommodate high-speed signal routing from the periphery of the ASIC. Examples are CPO, NPO and networking / broadband communication devices.

Vertical power delivery is the ultimate solution in terms of delivering very high current at low processor core voltages with the lowest PDN resistance. In this case, current multipliers and bypass capacitors are stacked on each other to form an integrated power module (geared current multiplier) that can be mounted directly underneath the processor by displacing the bypass capacitor bank. Vicor GCMs are custom-built devices that map the current multiplier pinouts to the AI processor BGA in addition to being able to provide all the bypass capacitor needs within the module itself. This technique opens up the top floor of the PCB for high-speed signal routing from the periphery of the processor to realize a solution with the highest signal integrity. Applications such as CPO (co-packaged optics, networking processors) and high-speed signaling ASICs can take advantage of this power delivery technique.

The Vicor architectures are flexible enough to be adapted a wide variety of high-performance computing solutions. Vicor solutions can reduce motherboard resistances up to 50x and processing power pin count more than 10x. Leveraging a Factorized Power Architecture (FPA™), Vicor minimizes the “last inch” resistances with patented solutions combining, lateral power delivery (LPD) and vertical power delivery (VPD). All enable processors to achieve previously unattainable performance levels to support today’s exponentially growing HPC processing demands.

The FPA architectures are unmatched in current density and in reducing power losses across the PDN. The propriety architectures, topologies and small module size are unique in the power industry. And for the next-generation processors to operate at full capacity they need a power solutions that that can adapt, scale and deliver high-density power. Robust, reliable power modules in conjunction with innovative topologies are essential in a dynamic systems where power requirements change rapidly. AI, machine learning and edge-computing will never have enough power for tomorrow using traditional power architectures. To meet that perpetual need you need to innovate today and be prepared to adapt and scale for tomorrow using modular power.

Open Compute Project and OCP are registered trademarks of the Open Compute Project.

FPA™ is a trademark of Vicor Corporation