WILSONVILLE, Ore., August 9, 2016 – Mentor Graphics Corp. (NASDAQ: MENT) has added to its Verification Academy a new SystemVerilog course and Patterns Library that together help verification engineers increase their expertise, productivity, and design quality. Developed by one of the leading SystemVerilog experts in the industry, SystemVerilog Object-Oriented Programming (OOP) for UVM Verification enables engineers to extend their SystemVerilog skills and keep up to date on the latest concepts, techniques, and methodologies. The searchable and versatile Patterns Library captures solutions for commonly encountered recurring problems, allowing organizations to document and share best practices to improve verification productivity and final design quality.

“The Verification Academy is a comprehensive, straightforward, and accessible resource for UVM-based verification. With the addition of the new Patterns Library, the Academy now provides an example-based, searchable library for verification design patterns,” said Brian Mathewson, lead ASIC verification engineer at SEAKR Engineering. “Supported by Mentor Graphics best-in-industry application engineers, the Verification Academy provides the resources needed to advance verification skills to speed up the design and verification cycle.”

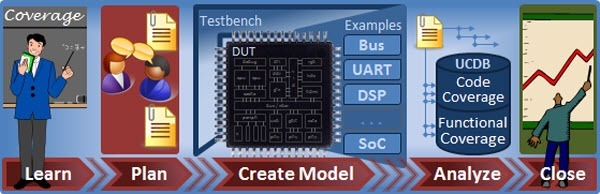

Design and verification patterns provide an optimized, reusable solution to many modern engineering problems. In verification, they are a proven, effective tool for sharing best practices and building skills within a project team. Mentor is broadening adoption of patterns by creating an easily searchable, readily available, and referenceable library that expands the application of patterns for verification. The new Patterns Library extends beyond the coding aspect of simulation testbenches into more general verification concerns, such as specifying assertions, defining input stimulus, and analysis. It reaches across the entire domain of verification—from specification to methodology to implementation. It introduces a systematic set of steps for organizing and documenting patterns in a manner that is applicable across all verification engines, including simulation and emulation.

SystemVerilog skills are in high demand. This new course is presented by recognized SystemVerilog expert Dave Rich, who was involved in the initial development of SystemVerilog and its standardization and continues to be a leading contributor to its expanding capabilities and value. The SystemVerilog OOP for UVM Verification course helps engineers grow their SystemVerilog skills so they can take advantage of the advanced verification tools and technologies demanded by the needs of the industry.

“With over 75% industry-wide adoption, SystemVerilog is now the predominant language used for verification today. Our new Verification Academy SystemVerilog course, along with our other popular UVM courses, provides an excellent educational resource for advancing verification skills,” said Harry Foster, chief scientist, Design Verification Technology Division at Mentor. “The new Verification Academy Patterns library provides provable solutions to many challenging assertion specification and UVM testbench problems—in an easily discoverable, referenceable, and relatable format.”